The problem persists after coral was removed.

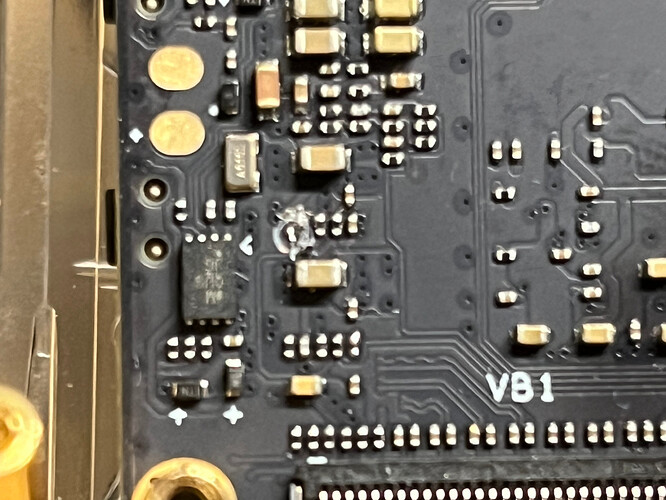

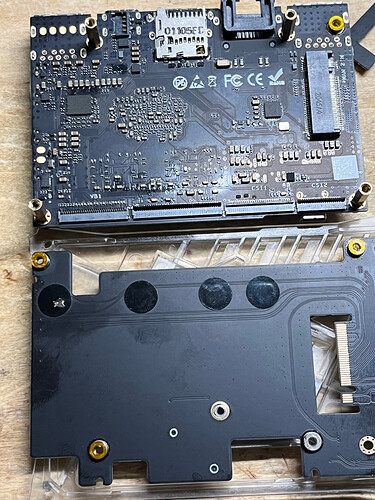

Here are photos and serial log.

BL2X 00053200 00011000

DDRFIP 00064200 00040000

DEVFIP 000a4200 00300000

s_setup from rom:00010081

dma mode

derive RSPK OK

DDR driver_vesion: AML_S_PHY_T7_1_18 build time: Sep 13 2022 15:55:10

ddr id: 0

ddr clk to 2016MHz

ch0 clk 2016

ch1 clk 2016PIEI done

Cfg max: 2, cur: 1. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

INFO : ERROR : Training has failed!

Check phy result

INFO : End of initialization

INFO : ERROR : Training has failed!

ch0 1D training failed

Load: DDRFIP From: eMMC - 3.0 src: 00000000, dst: f700ab90, size: 00001000

sdemmc src: ;

fw parse done

Cfg max: 2, cur: 2. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

T7:BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;eMMC:0;RD-1:0;CHK:1;RD-2:0;CHK:1;SPINOR:0;RD-0:0;CHK:0;SCS:0;

Bl2_early_platform_setup: indicates bl2ex flow!

failed to read efuse, set the default voltage:0.83v

0005000dfe05e000

OTP_LIC00 : 0f0300000000ff1f2f000b0000000000

OTP_LIC10 : 008207000001fc000c00001000000300

OTP_LIC20 : ffffffbfffff0700ff80008003000003

OTP_LIC30 : 00000002010000008f03000203000000

TE: 502348

BL2 Built : 15:55:21, Sep 13 2022. t7 origin/master g80f6117 - jenkins@walle02-sh

Board ID = 5

Set sys clock to 24Mhz

syspll is 1512Mhz. Locked

sys1pll is 1608Mhz. Locked

Set sys clock to 167Mhz

gp0pll is 0Mhz. Locked

bl2_platform_setup

boot area list:

1STBLOB 00000000 00040000

BL2E 00080000 00013000

BL2X 000a6000 00011000

DDRFIP 000c8000 00040000

DEVFIP 00148000 00300000

storage_spinor_init !

derive RSPK OK

DDR driver_vesion: AML_S_PHY_T7_1_18 build time: Sep 13 2022 15:55:10

ddr id: 0

ddr clk to 2016MHz

ch0 clk 2016

ch1 clk 2016PIEI done

Cfg max: 2, cur: 1. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

INFO : ERROR : Training has failed!

Check phy result

INFO : End of initialization

INFO : ERROR : Training has failed!

ch0 1D training failed

Load: DDRFIP From: SPINOR - 2.0 src: 00000000, dst: f700ab90, size: 00001000

;

fw parse done

Cfg max: 2, cur: 2. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

T7:BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;SPINOR:0;RD-1:0;CHK:1;USB:ADFUBL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:1;USB:0;RD-00:0;:4BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;SD:2002;eMMC:0;RD-0:0;CHK:0;SCS:0;

Bl2_early_platform_setup: indicates bl2ex flow!

failed to read efuse, set the default voltage:0.83v

0005000dfe05e000

OTP_LIC00 : 0f0300000000ff1f2f000b0000000000

OTP_LIC10 : 008207000001fc000c00001000000300

OTP_LIC20 : ffffffbfffff0700ff80008003000003

OTP_LIC30 : 00000002010000008f03000203000000

TE: 187148

BL2 Built : 15:55:21, Sep 13 2022. t7 origin/master g80f6117 - jenkins@walle02-sh

Board ID = 5

Set sys clock to 24Mhz

syspll is 1512Mhz. Locked

sys1pll is 1608Mhz. Locked

Set sys clock to 167Mhz

gp0pll is 0Mhz. Locked

bl2_platform_setup

boot area list:

1STBLOB 00000200 00040000

BL2E 00040200 00013000

BL2X 00053200 00011000

DDRFIP 00064200 00040000

DEVFIP 000a4200 00300000

s_setup from rom:00010081

dma mode

derive RSPK OK

DDR driver_vesion: AML_S_PHY_T7_1_18 build time: Sep 13 2022 15:55:10

ddr id: 0

ddr clk to 2016MHz

ch0 clk 2016

ch1 clk 2016PIEI done

Cfg max: 2, cur: 1. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

INFO : ERROR : Training has failed!

Check phy result

INFO : End of initialization

INFO : ERROR : Training has failed!

ch0 1D training failed

Load: DDRFIP From: eMMC - 3.0 src: 00000000, dst: f700ab90, size: 00001000

sdemmc src: ;

fw parse done

Cfg max: 2, cur: 2. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

T7:BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;eMMC:0;RD-1:0;CHK:1;RD-2:0;CHK:1;SPINOR:0;RD-0:0;CHK:0;SCS:0;

Bl2_early_platform_setup: indicates bl2ex flow!

failed to read efuse, set the default voltage:0.83v

0005000dfe05e000

OTP_LIC00 : 0f0300000000ff1f2f000b0000000000

OTP_LIC10 : 008207000001fc000c00001000000300

OTP_LIC20 : ffffffbfffff0700ff80008003000003

OTP_LIC30 : 00000002010000008f03000203000000

TE: 502630

BL2 Built : 15:55:21, Sep 13 2022. t7 origin/master g80f6117 - jenkins@walle02-sh

Board ID = 5

Set sys clock to 24Mhz

syspll is 1512Mhz. Locked

sys1pll is 1608Mhz. Locked

Set sys clock to 167Mhz

gp0pll is 0Mhz. Locked

bl2_platform_setup

boot area list:

1STBLOB 00000000 00040000

BL2E 00080000 00013000

BL2X 000a6000 00011000

DDRFIP 000c8000 00040000

DEVFIP 00148000 00300000

storage_spinor_init !

derive RSPK OK

DDR driver_vesion: AML_S_PHY_T7_1_18 build time: Sep 13 2022 15:55:10

ddr id: 0

ddr clk to 2016MHz

ch0 clk 2016

ch1 clk 2016PIEI done

Cfg max: 2, cur: 1. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

INFO : ERROR : Training has failed!

Check phy result

INFO : End of initialization

INFO : ERROR : Training has failed!

ch0 1D training failed

Load: DDRFIP From: SPINOR - 2.0 src: 00000000, dst: f700ab90, size: 00001000

;

fw parse done

Cfg max: 2, cur: 2. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

T7:BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;SPINOR:0;RD-1:0;CHK:1;USB:ADFUBL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:1;USB:0;RD-00:0;:4BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;SD:2002;eMMC:0;RD-0:0;CHK:0;SCS:0;

Bl2_early_platform_setup: indicates bl2ex flow!

failed to read efuse, set the default voltage:0.83v

0005000dfe05e000

OTP_LIC00 : 0f0300000000ff1f2f000b0000000000

OTP_LIC10 : 008207000001fc000c00001000000300

OTP_LIC20 : ffffffbfffff0700ff80008003000003

OTP_LIC30 : 00000002010000008f03000203000000

TE: 187240

BL2 Built : 15:55:21, Sep 13 2022. t7 origin/master g80f6117 - jenkins@walle02-sh

Board ID = 5

Set sys clock to 24Mhz

syspll is 1512Mhz. Locked

sys1pll is 1608Mhz. Locked

Set sys clock to 167Mhz

gp0pll is 0Mhz. Locked

bl2_platform_setup

boot area list:

1STBLOB 00000200 00040000

BL2E 00040200 00013000

BL2X 00053200 00011000

DDRFIP 00064200 00040000

DEVFIP 000a4200 00300000

s_setup from rom:00010081

dma mode

derive RSPK OK

DDR driver_vesion: AML_S_PHY_T7_1_18 build time: Sep 13 2022 15:55:10

ddr id: 0

ddr clk to 2016MHz

ch0 clk 2016

ch1 clk 2016PIEI done

Cfg max: 2, cur: 1. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

INFO : ERROR : Training has failed!

Check phy result

INFO : End of initialization

INFO : ERROR : Training has failed!

ch0 1D training failed

Load: DDRFIP From: eMMC - 3.0 src: 00000000, dst: f700ab90, size: 00001000

sdemmc src: ;

fw parse done

Cfg max: 2, cur: 2. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

T7:BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;eMMC:0;RD-1:0;CHK:1;RD-2:0;CHK:1;SPINOR:0;RD-0:0;CHK:0;SCS:0;

Bl2_early_platform_setup: indicates bl2ex flow!

failed to read efuse, set the default voltage:0.83v

0005000dfe05e000

OTP_LIC00 : 0f0300000000ff1f2f000b0000000000

OTP_LIC10 : 008207000001fc000c00001000000300

OTP_LIC20 : ffffffbfffff0700ff80008003000003

OTP_LIC30 : 00000002010000008f03000203000000

TE: 501867

BL2 Built : 15:55:21, Sep 13 2022. t7 origin/master g80f6117 - jenkins@walle02-sh

Board ID = 5

Set sys clock to 24Mhz

syspll is 1512Mhz. Locked

sys1pll is 1608Mhz. Locked

Set sys clock to 167Mhz

gp0pll is 0Mhz. Locked

bl2_platform_setup

boot area list:

1STBLOB 00000000 00040000

BL2E 00080000 00013000

BL2X 000a6000 00011000

DDRFIP 000c8000 00040000

DEVFIP 00148000 00300000

storage_spinor_init !

derive RSPK OK

DDR driver_vesion: AML_S_PHY_T7_1_18 build time: Sep 13 2022 15:55:10

ddr id: 0

ddr clk to 2016MHz

ch0 clk 2016

ch1 clk 2016PIEI done

Cfg max: 2, cur: 1. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

INFO : ERROR : Training has failed!

Check phy result

INFO : End of initialization

INFO : ERROR : Training has failed!

ch0 1D training failed

Load: DDRFIP From: SPINOR - 2.0 src: 00000000, dst: f700ab90, size: 00001000

;

fw parse done

Cfg max: 2, cur: 2. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

T7:BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;SPINOR:0;RD-1:0;CHK:1;USB:ADFUBL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:1;USB:0;RD-00:0;:4BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;SD:2002;eMMC:0;RD-0:0;CHK:0;SCS:0;

Bl2_early_platform_setup: indicates bl2ex flow!

failed to read efuse, set the default voltage:0.83v

0005000dfe05e000

OTP_LIC00 : 0f0300000000ff1f2f000b0000000000

OTP_LIC10 : 008207000001fc000c00001000000300

OTP_LIC20 : ffffffbfffff0700ff80008003000003

OTP_LIC30 : 00000002010000008f03000203000000

TE: 187379

BL2 Built : 15:55:21, Sep 13 2022. t7 origin/master g80f6117 - jenkins@walle02-sh

Board ID = 5

Set sys clock to 24Mhz

syspll is 1512Mhz. Locked

sys1pll is 1608Mhz. Locked

Set sys clock to 167Mhz

gp0pll is 0Mhz. Locked

bl2_platform_setup

boot area list:

1STBLOB 00000200 00040000

BL2E 00040200 00013000

BL2X 00053200 00011000

DDRFIP 00064200 00040000

DEVFIP 000a4200 00300000

s_setup from rom:00010081

dma mode

derive RSPK OK

DDR driver_vesion: AML_S_PHY_T7_1_18 build time: Sep 13 2022 15:55:10

ddr id: 0

ddr clk to 2016MHz

ch0 clk 2016

ch1 clk 2016PIEI done

Cfg max: 2, cur: 1. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

INFO : ERROR : Training has failed!

Check phy result

INFO : End of initialization

INFO : ERROR : Training has failed!

ch0 1D training failed

Load: DDRFIP From: eMMC - 3.0 src: 00000000, dst: f700ab90, size: 00001000

sdemmc src: ;

fw parse done

Cfg max: 2, cur: 2. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

T7:BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;eMMC:0;RD-1:0;CHK:1;RD-2:0;CHK:1;SPINOR:0;RD-0:0;CHK:0;SCS:0;

Bl2_early_platform_setup: indicates bl2ex flow!

failed to read efuse, set the default voltage:0.83v

0005000dfe05e000

OTP_LIC00 : 0f0300000000ff1f2f000b0000000000

OTP_LIC10 : 008207000001fc000c00001000000300

OTP_LIC20 : ffffffbfffff0700ff80008003000003

OTP_LIC30 : 00000002010000008f03000203000000

TE: 503188

BL2 Built : 15:55:21, Sep 13 2022. t7 origin/master g80f6117 - jenkins@walle02-sh

Board ID = 5

Set sys clock to 24Mhz

syspll is 1512Mhz. Locked

sys1pll is 1608Mhz. Locked

Set sys clock to 167Mhz

gp0pll is 0Mhz. Locked

bl2_platform_setup

boot area list:

1STBLOB 00000000 00040000

BL2E 00080000 00013000

BL2X 000a6000 00011000

DDRFIP 000c8000 00040000

DEVFIP 00148000 00300000

storage_spinor_init !

derive RSPK OK

DDR driver_vesion: AML_S_PHY_T7_1_18 build time: Sep 13 2022 15:55:10

ddr id: 0

ddr clk to 2016MHz

ch0 clk 2016

ch1 clk 2016PIEI done

Cfg max: 2, cur: 1. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

INFO : ERROR : Training has failed!

Check phy result

INFO : End of initialization

INFO : ERROR : Training has failed!

ch0 1D training failed

Load: DDRFIP From: SPINOR - 2.0 src: 00000000, dst: f700ab90, size: 00001000

;

fw parse done

Cfg max: 2, cur: 2. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

T7:BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;SPINOR:0;RD-1:0;CHK:1;USB:ADFUBL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:1;USB:0;RD-00:0;:4BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;SD:2002;eMMC:0;RD-0:0;CHK:0;SCS:0;

Bl2_early_platform_setup: indicates bl2ex flow!

failed to read efuse, set the default voltage:0.83v

0005000dfe05e000

OTP_LIC00 : 0f0300000000ff1f2f000b0000000000

OTP_LIC10 : 008207000001fc000c00001000000300

OTP_LIC20 : ffffffbfffff0700ff80008003000003

OTP_LIC30 : 00000002010000008f03000203000000

TE: 186830

BL2 Built : 15:55:21, Sep 13 2022. t7 origin/master g80f6117 - jenkins@walle02-sh

Board ID = 5

Set sys clock to 24Mhz

syspll is 1512Mhz. Locked

sys1pll is 1608Mhz. Locked

Set sys clock to 167Mhz

gp0pll is 0Mhz. Locked

bl2_platform_setup

boot area list:

1STBLOB 00000200 00040000

BL2E 00040200 00013000

BL2X 00053200 00011000

DDRFIP 00064200 00040000

DEVFIP 000a4200 00300000

s_setup from rom:00010081

dma mode

derive RSPK OK

DDR driver_vesion: AML_S_PHY_T7_1_18 build time: Sep 13 2022 15:55:10

ddr id: 0

ddr clk to 2016MHz

ch0 clk 2016

ch1 clk 2016PIEI done

Cfg max: 2, cur: 1. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

INFO : ERROR : Training has failed!

Check phy result

INFO : End of initialization

INFO : ERROR : Training has failed!

ch0 1D training failed

Load: DDRFIP From: eMMC - 3.0 src: 00000000, dst: f700ab90, size: 00001000

sdemmc src: ;

fw parse done

Cfg max: 2, cur: 2. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

T7:BL:055c20;ID:905660110991080D;FEAT:30F:1FFF0000:B002F:1;POC:CF;RCY:0;OVD:0;DFU:0;eMMC:0;RD-1:0;CHK:1;RD-2:0;CHK:1;SPINOR:0;RD-0:0;CHK:0;SCS:0;

Bl2_early_platform_setup: indicates bl2ex flow!

failed to read efuse, set the default voltage:0.83v

0005000dfe05e000

OTP_LIC00 : 0f0300000000ff1f2f000b0000000000

OTP_LIC10 : 008207000001fc000c00001000000300

OTP_LIC20 : ffffffbfffff0700ff80008003000003

OTP_LIC30 : 00000002010000008f03000203000000

TE: 502327

BL2 Built : 15:55:21, Sep 13 2022. t7 origin/master g80f6117 - jenkins@walle02-sh

Board ID = 5

Set sys clock to 24Mhz

syspll is 1512Mhz. Locked

sys1pll is 1608Mhz. Locked

Set sys clock to 167Mhz

gp0pll is 0Mhz. Locked

bl2_platform_setup

boot area list:

1STBLOB 00000000 00040000

BL2E 00080000 00013000

BL2X 000a6000 00011000

DDRFIP 000c8000 00040000

DEVFIP 00148000 00300000

storage_spinor_init !

derive RSPK OK

DDR driver_vesion: AML_S_PHY_T7_1_18 build time: Sep 13 2022 15:55:10

ddr id: 0

ddr clk to 2016MHz

ch0 clk 2016

ch1 clk 2016PIEI done

Cfg max: 2, cur: 1. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result

INFO : ERROR : Training has failed!

Check phy result

INFO : End of initialization

INFO : ERROR : Training has failed!

ch0 1D training failed

Load: DDRFIP From: SPINOR - 2.0 src: 00000000, dst: f700ab90, size: 00001000

;

fw parse done

Cfg max: 2, cur: 2. Board id: 255. Force loop cfg

LPDDR4 probe

ddr clk to 2016MHz

Check phy result