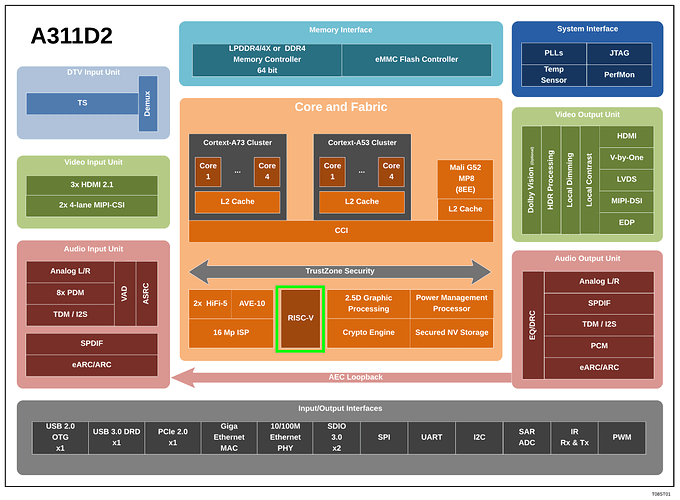

Looking at the datasheet for the A311D2, there is a RISC-V CPU available, but the datasheet doesn’t have any details other than interrupt line descriptions (amrisc_*). Is there any details/specifications and/or application notes available for the RISC-V core in the VIM4 SoC?

Hello @jkiepert

We don’t have such documentations.

By the way, you can get the source for RISV-V MCU here:

@numbqq Thanks for the link to the MCU source, that is very helpful. Just to be clear, is the RISC-V a general purpose MCU available for use after the main CPUs are up and running or does it remain in use by the SoC after Linux boot to manage SoC operation?

from the code it seems like the risc-v core is just the same as the cortex-M used in other SoCs for handling miscellaneous SoC operations like power handling, led control, gpio management etc.

The purpose of the Cortex-M cores depends greatly on the particular SoC. Some SoCs use it for boot code and system management without any option to write your own firmware for it. On the other hand, SoCs like the NXP i.MX8 series, for example, have a Cortex-M (M4 or M7) which is fully documented and may be enabled to run a developer’s RTOS along side Linux. This is the use case I’m interested in achieving on the VIM4. Linux interrupt latency can be terrible for real-time I/O (> 30 ms), so it would be useful to have a RTOS running on the RISC-V to manage real-time I/O with some external devices. Ideally, there would also be a hardware mailbox in the SoC to enable IPC between the RISC-V and the Cortex-A cluster as well. This way you can develop Linux applications that interact with the RTOS running on the real-time MCU.

Yes, the FAN is controlled by onboard STM32 MCU.